Product Summary

This Hynix unbuffered Small Outline Dual In-Line Memory Module(DIMM) HYMP125S64CP8-S6 consists of 1Gb version C DDR2 SDRAMs in Fine Ball Grid Array(FBGA) packages on a 200pin glass-epoxy substrate. This Hynix 1Gb version C based Unbuffered DDR2 SO-DIMM series provide a high performance 8 byte interface in 67.60mm width form factor of industry standard. HYMP125S64CP8-S6 is suitable for easy interchange and addition.

Parametrics

HYMP125S64CP8-S6 absolute maximum ratings: (1)Voltage on VDD pin relative to Vss VDD: -1.0 V ~ 2.3 V; (2)Voltage on VDDQ pin relative to Vss VDDQ: -0.5 V ~ 2.3 V; (3)Voltage on VDDL pin relative to Vss VDDL: -0.5V ~ 2.3 V; (4)Voltage on any pin relative to Vss VIN, VOUT: - 0.5 V ~ 2.3 V.

Features

HYMP125S64CP8-S6 features: (1)JEDEC standard Double Data Rate 2 Synchronous DRAMs (DDR2 SDRAMs) with 1.8V +/- 0.1V Power Supply; (2)All inputs and outputs are compatible with SSTL_1.8 interface; (3)Posted CAS; (4)Programmable CAS Latency 3 ,4 ,5, and 6; (5)OCD (Off-Chip Driver Impedance Adjustment) and ODT (On-Die Termination); (6)Fully differential clock operations (CK & CK); (7)Programmable Burst Length 4 / 8 with both sequential and interleave mode; (8)Auto refresh and self refresh supported; (9)8192 refresh cycles / 64ms; (10)Serial presence detect with EEPROM; (11)DDR2 SDRAM Package: 60 ball(x8) , 84 ball(x16) FBGA; (12)67.60 x 30.00 mm form factor; (13)RoHS compliant.

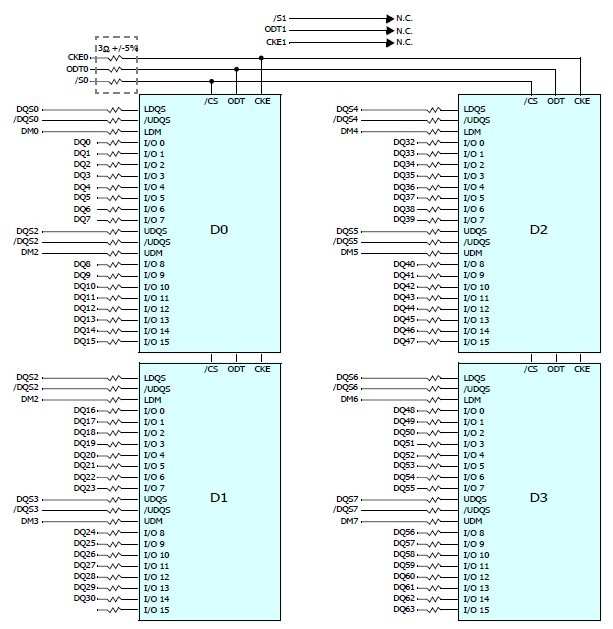

Diagrams

|

HYMP512R724 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYMP512R72L4 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYMP564R72P8-E3 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYMP564S648-E3/C4 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYMP564R72P8-C4 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYMP564R728-E3 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))