Product Summary

The R5S72631P200BG is a single-chip RISC (reduced instruction set computer) microcontroller that includes a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system. The R5S72631P200BG has a floating-point unit (FPU) and cache. It also provides an external memory access support function to enable direct connection to various memory devices or peripheral LSIs. These on-chip functions significantly reduce costs of designing and manufacturing application systems. Furthermore, I/O pins in the R5S72631P200BG have weak keeper circuits that prevent the pin voltage from entering an intermediate potential range. Therefore, no external circuits to fix the input level are required, which reduces the parts number considerably.

Parametrics

R5S72631P200BG absolute maximum ratings: (1)Power supply voltage (Internal):-0.3V to 1.7V ; (2)PLL power supply voltage:-0.3V to 1.7V ; (3)Analog power supply voltage:-0.3V to 4.6V ; (4)Analog reference voltage:-0.3V to AVCC +0.3V ; (5)USB transceiver analog power supply voltage:-0.3V to 4.6V ; (6)USB transceiver digital power supply:-0.3V to 4.6V ; (7)USB transceiver analog power supply voltage (internal):-0.3V to 1.7V ; (8)USB transceiver digital power supply voltage (internal):-0.3V to 1.7V ; (9)Input voltage:Analog input pin:-0.3V to AVCC +0.3 V,VBUS:-0.3V to 5.5V,Other input pins:-0.3V to PVCC +0.3V ; (10)Operating temperature:-40℃ to +85℃; (11)Storage temperature:-55℃ to +125℃.

Features

R5S72631P200BG features: (1)Renesas Technology original SuperH architecture ; (2)Compatible with SH-1, SH-2, and SH-2E at object code level ; (3)32-bit internal data bus ; (4)Support of an abundant register-set ; (5)Superscalar architecture to execute two instructions at one time including FPU ; (6)Instruction execution time: Up to two instructions/cycle ; (7)Address space: 4 Gbytes ; (8)Internal multiplier ; (9)Five-stage pipeline ; (10)Harvard architecture; (11)Floating-point co-processor included ; (12)Supports single-precision (32-bit) and double-precision (64-bit) ; (13)Supports data type and exceptions that conforms to IEEE754 standard; (14)Two rounding modes: Round to nearest and round to zero ; (15)Two denormalization modes: Flush to zero ; (16)Floating-point registers ; (17)Supports FMAC (multiplication and accumulation) instructions ; (18)Supports FDIV (division) and FSQRT (square root) instructions ; (19)Supports FLDI0/FLDI1 (load constant 0/1) instructions ; (20)Instruction cache: 8 Kbytes ; (21)Operand cache: 8 Kbytes ; (22)128-entries/way, 4-way set associative, 16-byte block length configuration ; (23)Write-back, write-through, LRU replacement algorithm ; (24)Way-lock function available (operand cache only): ways 2 and 3 can be locked .

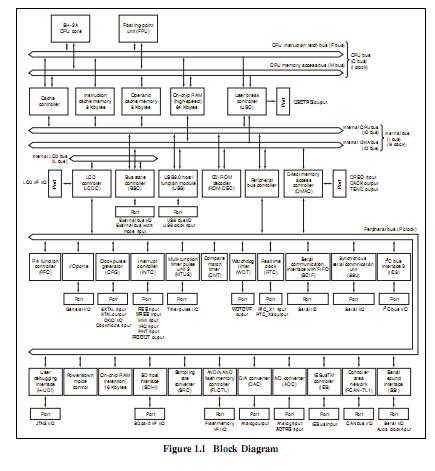

Diagrams

|

R5S72030W200FP |

|

IC SUPERH MPU ROMLESS 240QFP |

Data Sheet |

Negotiable |

|

||||||||||||||||||||||

|

R5S72620P144FP#UZ |

|

MPU 1M RAM 144MHZ 176-QFP |

Data Sheet |

|

|

||||||||||||||||||||||

|

R5S72620W144FP#U0 |

|

MPU 1M RAM 144MHZ 176-QFP |

Data Sheet |

|

|

||||||||||||||||||||||

|

R5S72621P144FP#UZ |

|

MPU 1M RAM 144MHZ 176-QFP |

Data Sheet |

|

|

||||||||||||||||||||||

|

R5S72621W144FP#U0 |

|

MPU 1M RAM 144MHZ 176-QFP |

Data Sheet |

|

|

||||||||||||||||||||||

|

R5S72624P144FP#UZ |

|

MPU 640K RAM 144MHZ 176-QFP |

Data Sheet |

|

|

||||||||||||||||||||||

(China (Mainland))

(China (Mainland))